Vhdl Program For 8 Bit Up Down Counter Diagram

An up/down counter is written in VHDL and implemented on a CPLD. The VHDL while loop as well as VHDL generic are also demonstrated. Four different VHDL up/down counters are created in this tutorial: • Up/down counter that counts up to a maximum value and then wraps around to 0.

Counts down to 0 and then wraps around to a maximum value. • Up/down counter that counts up to a maximum limit then stops. Counts down to 0 then stops.

Vhdl Program For 8 Bit Up Down Counter Vhdl. Ripple Counter - Basic Digital Electronics Course. Prerequisite Pages. The D flip flop is a basic building block of. This page contains VHDL tutorial, VHDL Syntax, VHDL Quick Reference, modelling memory and FSM, Writing Testbenches in VHDL. 8-Bit Up-Down Counter. SYNCHRONOUS 8-BIT UP/DOWN COUNTERS. The function of the counter (whether enabled, disabled. Old Hindi Mp3 Songs Free Download Zip File here. Logic diagram (positive logic) A 1D R C1 22 QA 14 1.

Demonstrates the VHDL while loop. • Up/down counter that demonstrates the use of a single VHDL generic.

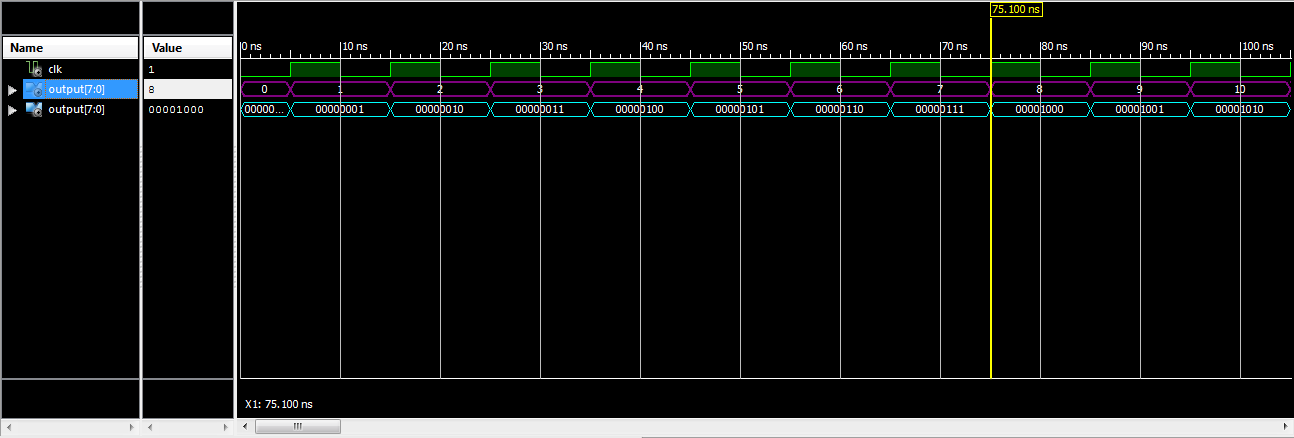

• Up/down counter that demonstrates the use of two VHDL generic values. Continuous Up/Down Counter This counter will continuously count up and wrap around to 0 when the maximum value is reached if the direction input to the counter is set to count up. The counter will continuously count down and wrap around to the maximum value when 0 is reached if the direction input to the counter is set to count down. This video shows the continuous up/down counter in operation. Can't see the video? Can't see the video? VHDL Code for up_dn_counter2 The VHDL code for the up/down counter with limits is shown here.

Library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity up_down_counter2 is Port ( CLK: in STD_LOGIC; DIR: in STD_LOGIC; LED: out STD_LOGIC_VECTOR (7 downto 0)); end up_down_counter2; architecture Behavioral of up_down_counter2 is signal clk_div: STD_LOGIC_VECTOR (5 downto 0); signal count: STD_LOGIC_VECTOR (7 downto 0); begin -- clock divider process (CLK) begin if (CLK'Event and CLK = '1') then clk_div 0) loop count. Up/Down Counter using One VHDL Generic A generic is a named value that is put in the entity part of the VHDL code. Wherever the name of the generic value is used in the VHDL code, its value will be substituted. A generic is similar to using #define in a C program. Generics are useful for: • Changing a value that occurs in more than one place in the VHDL code. By changing the value of the generic in the entity part of the code, every place that the generic occurs in the rest of the code will be changed to its new value. • Making it possible to change a value near the top of a file, even if the value occurs anywhere else in the file.

Comments are closed.